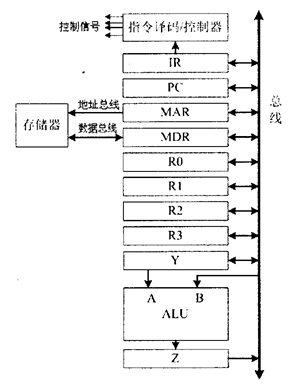

设有单总线结构计算机的CPU数据通路及其与存储器的连接结构如下图所示。其中, R0~R3为通用寄存器,IR为指令寄存器,PC为程

设有单总线结构计算机的CPU数据通路及其与存储器的连接结构如下图所示。其中, R0~R3为通用寄存器,IR为指令寄存器,PC为程序计数器,MAR为存储器地址寄存器,MDR为存储器数据缓冲寄存器。试写出减法指令SUB R3,R2,Rl的执行流程。指令功能为将R2和Rl中的数据相加减,结果送到寄存器R3中存放。

【正确答案】:(1)送入指令地址:PC→MAR

(2)计算机下一条指令地址:PC+1→PC

(3)读入指令:DBUS→MDR、MDR→IR

(4)送第一个操作数R2→Y

(5)送第二个操作数并做减法Rl-Y→Z

(6)送结果Z→R3